## Advanced VLSI Design Why Power Matters

- Packaging costs

- Power supply rail design

- Chip and system cooling costs

- Noise immunity and system reliability

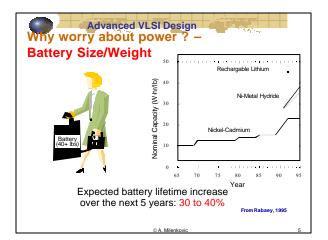

- Battery life (in portable systems)

- Environmental concerns

- Office equipment accounted for 5% of total US commercial energy usage in 1993

© A. Milenkovid

Energy Star compliant systems

© A. Milenkovic

|                                                   | CL018   | CL018   | CL018   | CL018   | CL015   | CL013   |

|---------------------------------------------------|---------|---------|---------|---------|---------|---------|

| V <sub>dd</sub>                                   | 1.8 V   | 1.8 V   | 1.8 V   | 2 V     | 1.5 V   | 1.2 V   |

| T <sub>ox</sub> (effective)                       | 42 Å    | 42 Å    | 42 Å    | 42 Å    | 29 Å    | 24 Å    |

| date                                              | 0.16 µm | 0.16 µm | 0.18 µm | 0.13 µm | 0.11 µm | 0.08 µm |

| <sub>DSat</sub> (n/p)<br>(µA/µm)                  | 600/260 | 500/180 | 320/130 | 780/360 | 860/370 | 920/400 |

| l <sub>off</sub> (leakage)<br>( <del>pA/μm)</del> | 20      | 1.60    | 0.15    | 300     | 1,800   | 13,000  |

| V <sub>Tn</sub>                                   | 0.42 V  | 0.63 V  | 0.73 V  | 0.40 V  | 0.29 V  | 0.25 V  |

| FET Perf.                                         | 30      | 22      | 14      | 43      | 52      | 80      |

|         | nd Energy Design<br>Constant                               |                               | Variable        |                                                   |

|---------|------------------------------------------------------------|-------------------------------|-----------------|---------------------------------------------------|

| Energy  | Design Time                                                |                               |                 | put/Latency<br>Run Time                           |

| Active  | Reduced V <sub>dd</sub><br>Sizing<br>Multi V <sub>dd</sub> | Clock Gating                  |                 | DFS, DVS<br>(Dynamic<br>Freq, Voltage<br>Scaling) |

| Leakage | + Multi-V <sub>T</sub>                                     | Sleep Tra<br>Multi-<br>Variab | V <sub>dd</sub> | + Variable V <sub>1</sub>                         |

|         |                                                            |                               |                 |                                                   |

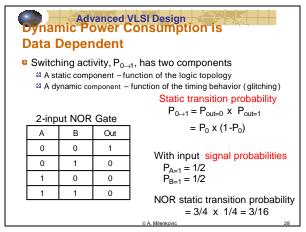

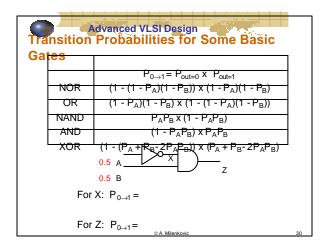

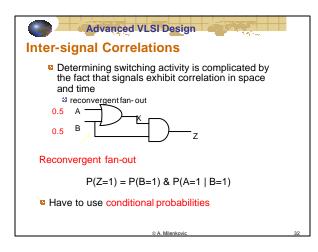

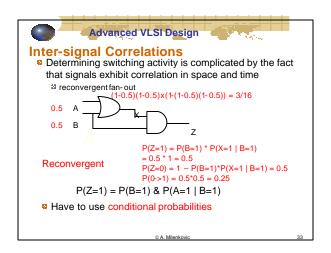

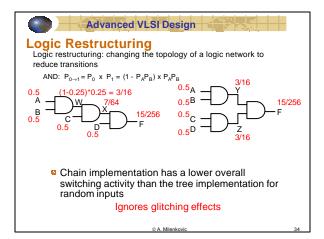

| Tra |      | Advanced VLSI Design<br>Probabilities for Some Basic                                                                                        |    |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

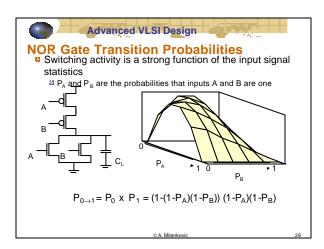

| Ga  | 105  | $P_{0 \rightarrow 1} = P_{out=0} \times P_{out=1}$                                                                                          |    |

|     | NOR  | (1 - (1 - P <sub>A</sub> )(1 - P <sub>B</sub> )) x (1 - P <sub>A</sub> )(1 - P <sub>B</sub> )                                               |    |

|     | OR   | (1 - P <sub>A</sub> )(1 - P <sub>B</sub> ) x (1 - (1 - P <sub>A</sub> )(1 - P <sub>B</sub> ))                                               |    |

|     | NAND | $P_A P_B x (1 - P_A P_B)$                                                                                                                   |    |

|     | AND  | $(1 - P_A P_B) \times P_A P_B$                                                                                                              |    |

|     | XOR  | $(1 - (P_A + P_B - 2P_AP_B)) \times (P_A + P_B - 2P_AP_B)$                                                                                  |    |

|     |      | $\begin{array}{c c} 0.5 & A \\ \hline \\ 0.5 & B \\ \hline \\ \end{array} \\ \hline \\ \end{array} \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$ |    |

|     | For  | X: $P_{0\to1} = P_0 \times P_1 = (1-P_A) P_A$<br>= 0.5 x 0.5 = 0.25                                                                         |    |

|     | For  | Z: $P_{0 \rightarrow 1} = P_0 \times P_1 = (1 - P_X P_B) P_X P_B$<br>= $(1 - (0.5 \times 0.5)) \times (0.5 \times 0.5) = 3/16$              |    |

|     |      | © A. Milenkovic                                                                                                                             | 31 |

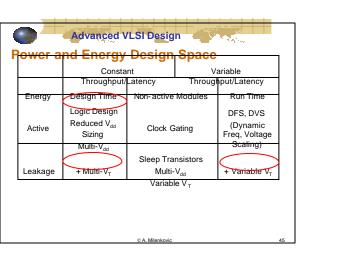

| Power a | Advanced V<br>nd Energy                                                    |                                                           | -       |                                                   |  |  |

|---------|----------------------------------------------------------------------------|-----------------------------------------------------------|---------|---------------------------------------------------|--|--|

|         | Consta<br>Throughput/                                                      |                                                           |         | Variable<br>Throughput/Latency                    |  |  |

| Energy  | Design Time                                                                | Non-active                                                | Modules | Run Time                                          |  |  |

| Active  | Logic Design<br>Reduced V <sub>dd</sub><br>Sizing<br>Multi V <sub>dd</sub> | Clock Gating                                              |         | DFS, DVS<br>(Dynamic<br>Freq, Voltage<br>Scaling) |  |  |

| Leakage | + Multi-V <sub>T</sub>                                                     | Sleep Transistors<br>Multi-V <sub>dd</sub><br>Variable Vr |         | + Variable V <sub>T</sub>                         |  |  |

|         |                                                                            |                                                           | ·       |                                                   |  |  |

## Advanced VLSI Design

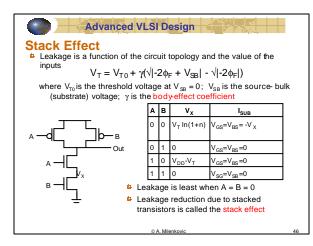

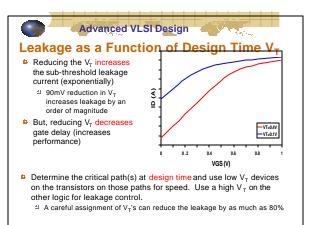

## Short Channel Factors and Stack Effect In short-channel devices, the subthreshold leakage current depends on V<sub>CS</sub>, V<sub>BS</sub> and V<sub>DS</sub>. The V<sub>T</sub> of a short-channel device decreases with increasing V<sub>DS</sub> due to DIBL (drain-induced barrier loading). <sup>43</sup> Typical values for DIBL are 20 to 150mV change in V<sub>T</sub> per voltage change in V<sub>DS</sub> so the stack effect is even more significant for short-channel devices. <sup>43</sup> V<sub>X</sub> reduces the drainsource voltage of the top nfet, increasing its V<sub>T</sub> and lowering its leakage

<sup>III</sup> For our 0.25 micron technology, V<sub>X</sub> settles to ~100mV in steady state so V<sub>BS</sub> = -100mV and V<sub>DS</sub> = V<sub>DD</sub> -100mV which is 20 times smaller than the leakage of a device with V<sub>BS</sub> = 0mV and V<sub>DS</sub> = V<sub>DD</sub>

© A. Milenkovid

© A. Milenkovi